Les événements de la communauté

Réalisations 2018-2019 et Perspectives 2019 : ICI

Les communautés partenaires

La COMET Informatique et Réseaux Embarqués (ex-CCT IRE) a organisé un seminaire ayant pour sujet « les composants FPGA et SoC du futur » qui s'est déroulé le 24 Janvier 2019 sur le site de l’ISAE Supaero à Toulouse.

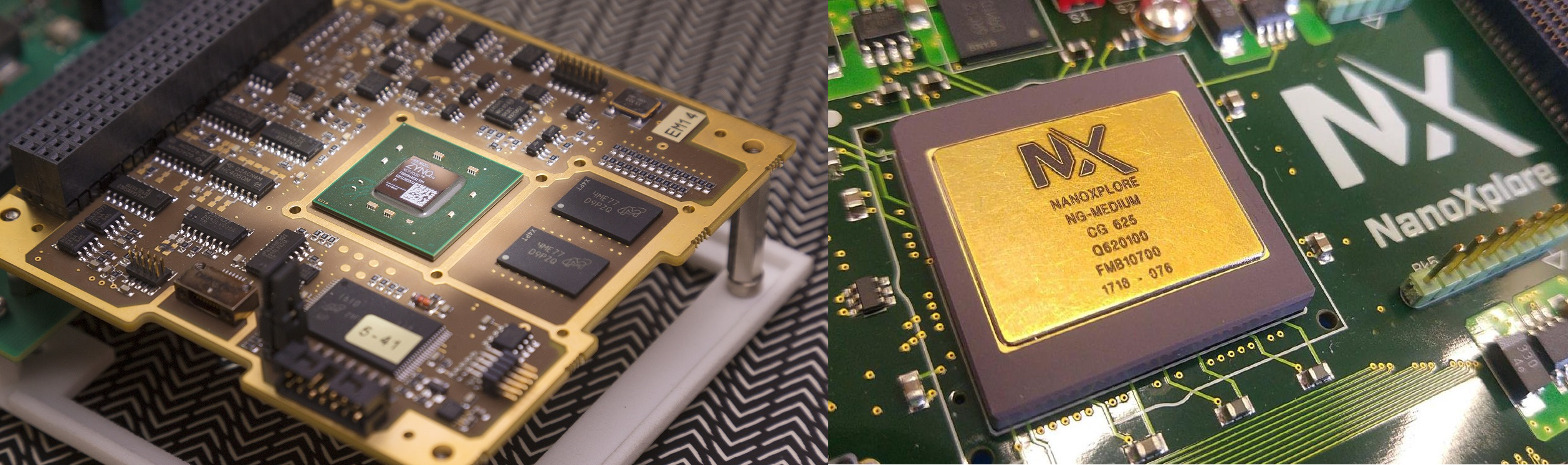

(a gauche, Ninano: © CNES/Gwenewan Le Bras; à droite, NanoXplore Medium © CNES/Mathieu Albinet)

Dans le domaine des calculateurs, les FPGAs tiennent une place très importante. Avec l’arrivée des System-on-Chip et de nouvelles filières FPGA dans les industries aéronautiques, spatiales et automobiles, la COMET IRE a souhaité inviter les différents acteurs du domaine à partager et à échanger sur leurs travaux.

Le seminaire a traité des questions suivantes :

- Utilisation des FPGAs dans les dernières missions scientifiques en France et dans le monde

- Nouvelles applications des FPGAs et SoCs dans l’industrie spatiale

- Validation de code et de bitstream pour les SoC embarqués dans les systèmes aéronautiques

- Validation formelle de code VHDL et génération de VHDL à partir de descriptions haut niveau

- Et aussi la présentation, par leur fabricants, de composants FPGA et SoC prochainement disponibles

Présentations

Introduction et nouveaux composants

- NanoXplore : Composant NG-Large, logiciel NanoXmap et NG-Ultra (J. LE MAUFF)

- Xilinx: Cartes Alveo pour traitements sol à base de SoC Ultrascale+ et roadmap (M. ROCCA)

Equipements embarqués à base de SoC et FPGA

- Airbus DS : Solutions modulaires VPX et bus haut débit sur composant Zynq/Kintex/Ultrascale+/DAHLIA (M. DOLLON)

- Airbus DS : Plateforme de traitement bord de haute performance à base de FPGA/MPSoC et applications (SDR, Navigation automatique, Image) (L. BARTHE)

Programmation et validation des logiciels pour SoC et FPGA

- Thales AS : Evaluation et utilisation de NanoXmap (G. GRIMONET)

- ONERA : Vérification formelle sémantique de code VHDL et génération de code à partir de langages haut niveau, LUSTRE ou SIMULINK (A. DIEUMEGARD)

- ASSystem : Vérification de code pour composant SoC en applications aéronautiques (JF. BACARDATZ)

Applications et missions scientifiques

- IRAP : Utilisation du NG-Medium dans le cadre de la mission SVOM (D. RAMBAUD)

- IRAP : Utilisation du FPGA Xilinx KU060 dans le cadre des traitements bord de la mission ATHENA X-IFU (L. RAVERA)